Honeywell

SERIES 16

MODELS 316 AND 516 SUMMARY DESCRIPTION

|  |   |    |  | 1 |

|--|---|----|--|---|

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  | d |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  | A |

|  |   |    |  |   |

|  | * |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

|  |   | 65 |  |   |

|  |   |    |  |   |

|  |   |    |  |   |

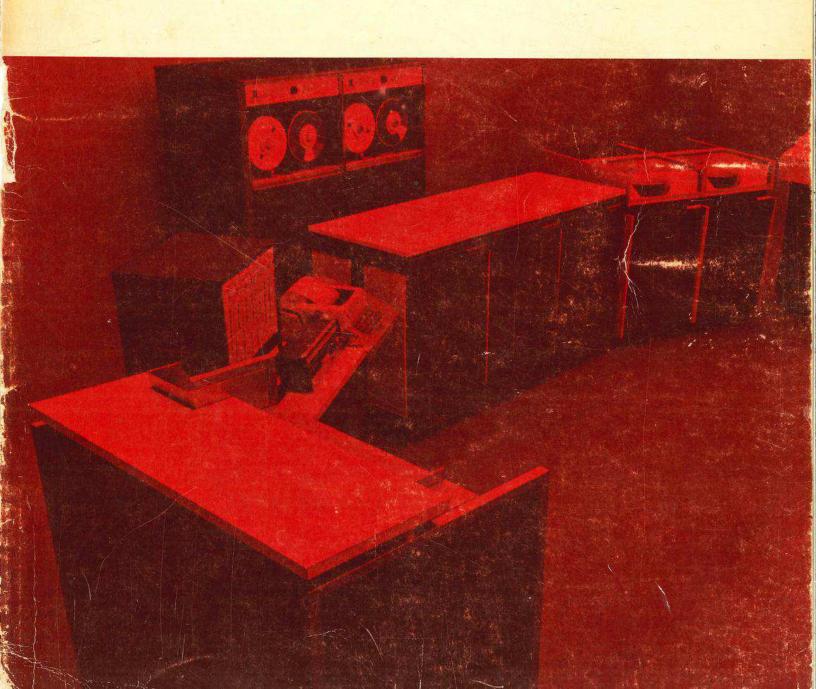

SERIES 16 MODELS 316 AND 516 SUMMARY DESCRIPTION

## **FOREWORD**

The Series 16 Models 316 and 516 Summary Description is intended for those having a general familiarity with data processing. Machine characteristics and programming aids are described in terms that should aid comparisons between these systems and competitive equipment. The equipment characteristics reported herein remain subject to revision in order that design improvements may be incorporated.

Section 1 discusses many of the problems faced by the minicomputer system designer and introduces the answers provided by the Series 16. Section 2 contains a detailed description of the Series 16, 1600, 1620, and 1640 packaged solutions. All of the individual components that comprise the Series 16 are discussed in Section 3. Finally, the appendix to this summary illustrates and describes the Series 16 instruction set, one of the primary reasons that the Series 16 is such an excellent answer to many control and communications problems.

# TABLE of CONTENTS

| INDEE OF CONTENTS                                        | Model 516R 29                                |

|----------------------------------------------------------|----------------------------------------------|

|                                                          | Model 316R 29                                |

| MINICOMPUTERS AND INFORMATION     PROCESSING 1           | Model 1602R 30 .                             |

| Money Matters 2                                          | 3. SERIES 16'S BUILDING BLOCKS 35            |

| Time Is Money 2                                          | Central Processors 35                        |

| Reliability; Specifications in General; the Real World 3 | Organization 35 Memory 35                    |

| Systems Support 4                                        | Control Registers 38                         |

| Design Support 4                                         | Arithmetic Registers 39                      |

| Implementation Support 4                                 | Input/Output Facilities 39                   |

| Post-Installation Support 5                              | Operation 42                                 |

| The Applications Themselves 5                            | Memory-Access Priority Capability 42         |

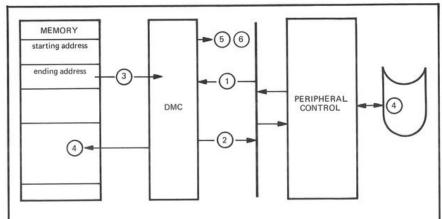

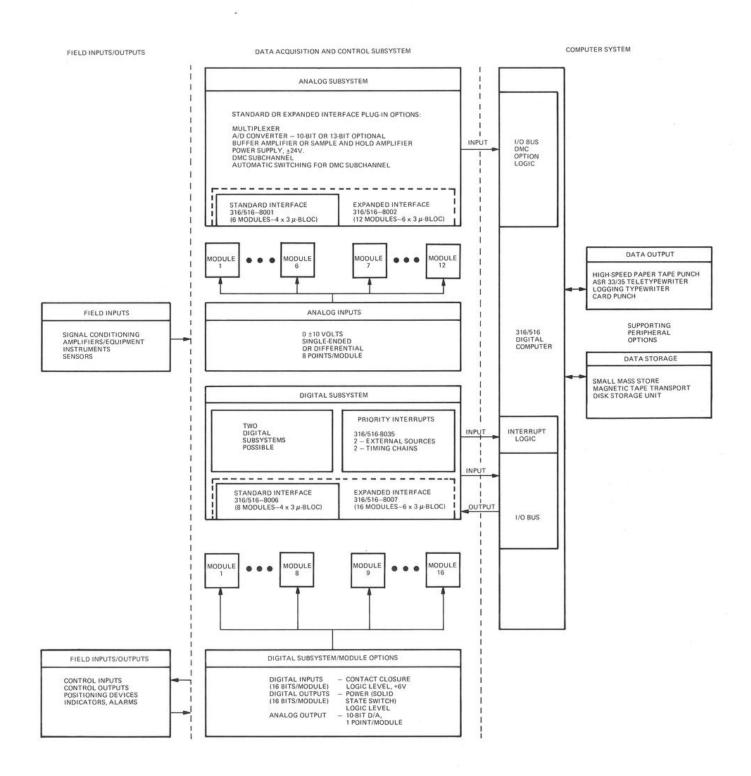

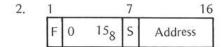

| Data Communications 5                                    | Word Formats 44                              |

| Data Acquisition and Control 8                           | Data Word 44                                 |

| Computer Timesharing 10                                  | Byte Word 44                                 |

| The Tools Themselves 12                                  | Single Precision Number 44                   |

| What Are the Tools? 12                                   | Double Precision Number 44                   |

| Processors 12                                            | Memory Reference Instruction 44              |

| Input/Storage/Control/Output                             | Input/Output Instruction 44                  |

| Interfaces 13                                            | Shift Instruction 44                         |

| Software 13                                              | Generic Instruction 44                       |

| Support 14                                               | Other Capabilities 46                        |

| Education 14                                             | High-Speed Arithmetic Package 46             |

| Publications 14                                          | Real-Time Clock 46                           |

| Data Centers 15                                          | Priority Interrupt, Memory Increment 46      |

| Systems Support Service 15                               | Memory Lockout 46                            |

| Field Maintenance 15                                     | Extended Addressing 46                       |

| What Can the Tools Do?                                   | On-Line Interfaces 46                        |

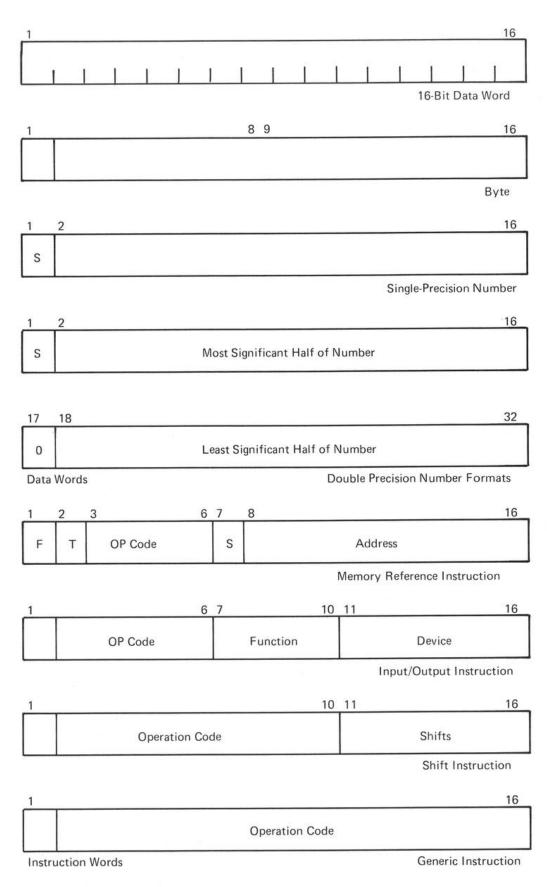

|                                                          | Data Acquisition and Control Subsystem 46    |

| 2. SERIES 16'S TOTAL SOLUTIONS 19                        | Model 8000 47                                |

| Series 1600 —                                            | Communications Interfaces 50                 |

| Data Acquisition and Control Systems 20                  | Data Line Controllers 50                     |

| Organization 21                                          | Multi-Line Controllers 53                    |

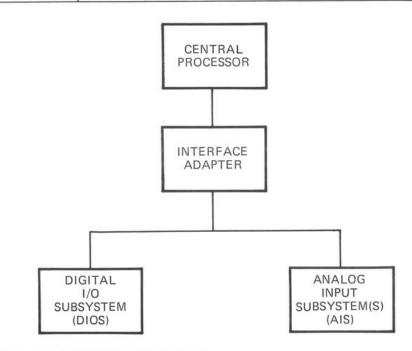

| Digital Input/Output Subsystem (DIOS) 21                 | Multi-Line Programmed Controllers 54         |

| Analog Input Subsystem (AIS) 21                          | Custom Built Interfaces 55                   |

| Series 1620 —                                            | Core Memory Systems 55                       |

| Remote Message Concentrator Systems 22                   | Digital Logic Modules 55                     |

| Timesharing Systems 24                                   | Analog Interface Modules 55                  |

| Model 1642 26                                            | Hardware, Power Supplies, and Accessories 56 |

| Model 1644 26                                            | Peripherals 56                               |

| Model 1646 26                                            | Disk Devices 56                              |

| Model 1648A 26                                           | Magnetic Tape Units 58                       |

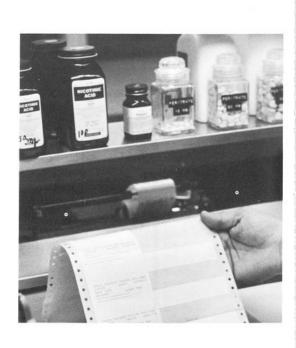

| Computer Assisted Clinical Laboratory System 28          | 7-Track Tape Units 58                        |

Ruggedized Systems 29

| 9-Track Tape Units 60                             | Logic 90                                       |

|---------------------------------------------------|------------------------------------------------|

| 9-Track Tape Units 60 Line Printers 61            | Logical And To A, ANA 90                       |

| Display Devices 61                                | Copy Sign and Set Sign Plus, CSA 90            |

| Type 7210 62                                      | Complement The Sign of A, CHS 92               |

| Type 7210 62 Type 7205, -6, -7 62                 | Complement The A Register, CMA 92              |

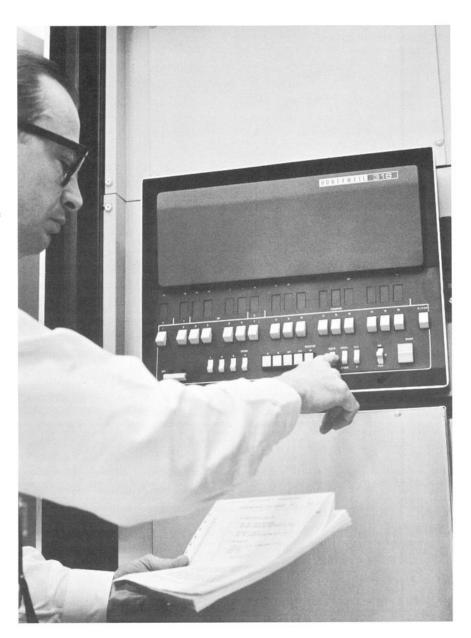

| Operator's Console 63                             | Exclusive Or To A, ERA 92                      |

|                                                   | Set Sign Minus, SSM 94                         |

| Card Equipment 63 Type 5121 63                    | Set Sign Plus, SSP 94                          |

| 20 <b>*</b> 0 * 0 * 0 * 0 * 0 * 0 * 0 * 0 * 0 * 0 | Shift 96                                       |

| Type 5140 63                                      | Logical Left Rotate, ALR 96                    |

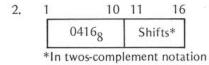

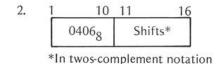

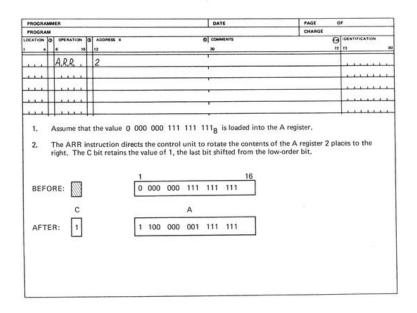

| Paper Tape Equipment 64                           | Logical Right Rotate, ARR 96                   |

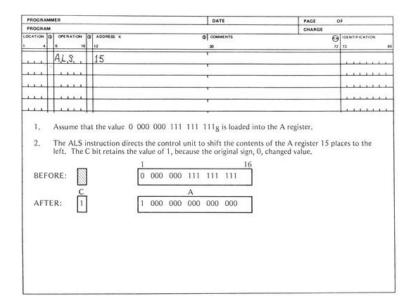

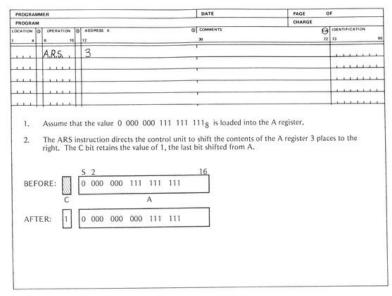

| Type 50, Paper Tape Reader 64                     | Arithmetic Left Shift, ALS 98                  |

| Type 52, Paper Tape Punch 64                      | Arithmetic Right Shift, ARS 98                 |

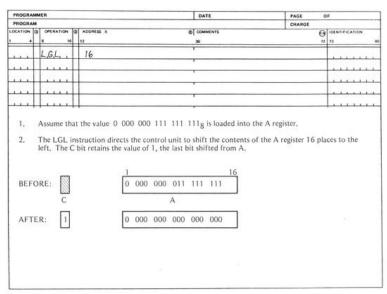

| Teletypewriters 64  Mechanical Accessories 65     | Logical Left Shift, LGL 98                     |

| Terminals 65                                      | Logical Right Shift, LGR 100                   |

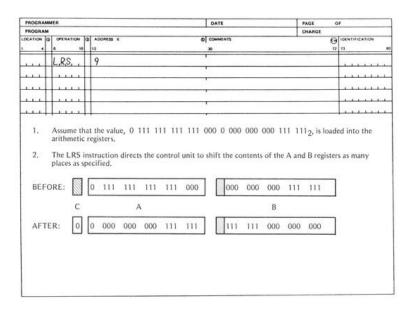

| V 50 00 00 00 00 00 00 00 00 00 00 00 00          | Long Arithmetic Right Shift, LRS 100           |

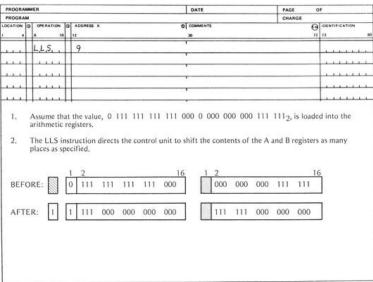

| Systems Software 69                               | Long Arithmetic Left Shift, LLS 101            |

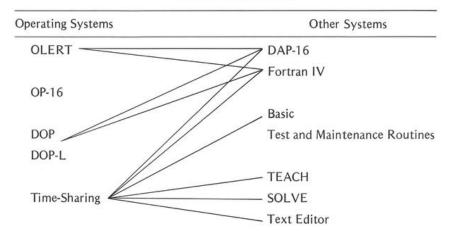

| Operating Programs 69 OLERT 69                    | Long Right Logical Shift, LRL 102              |

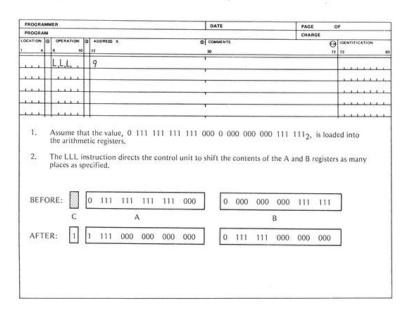

|                                                   | Long Left Logical Shift, LLL 102               |

| OP-16 Operating System 69                         | Long Left Rotate, LLR 102                      |

| Disk Operating Program (DOP) 70                   | Long Right Rotate, LRR 104                     |

| Languages 70                                      | Byte-Handling 104                              |

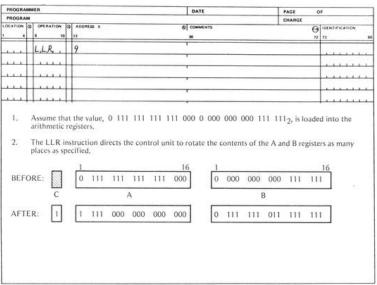

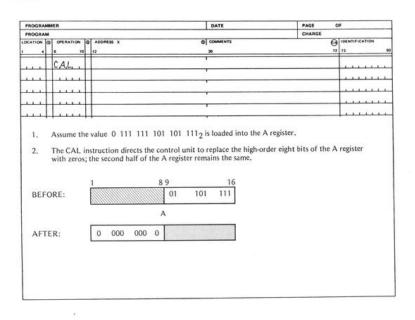

| Fortran IV 70                                     | Clear Left Half of A, CAL 105                  |

| BASIC Interpreter 70                              | Clear Right Half of A, CAR 106                 |

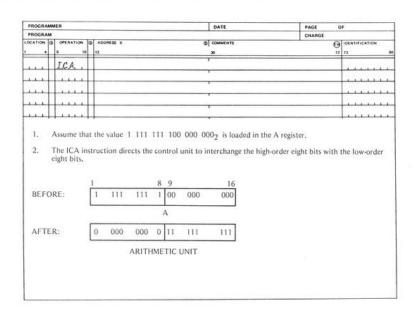

| Dap 16 Mod 2 Assembler 70                         | Interchange Characters In A, ICA 106           |

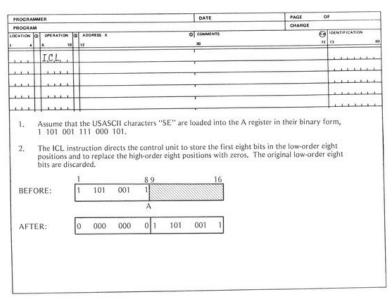

| Program Characteristics 71                        | Interchange and Clear Left Half of A, ICL 106  |

| Utility Programs 71                               | Interchange and Clear Right Half of A, ICR 108 |

| Test and Maintenance Routines 72                  | Control 108                                    |

| APPENDIX:                                         | Compare, CAS 109                               |

| PROGRAMMING THE SERIES 16 75                      | Increment, Replace, and Skip, IRS 110          |

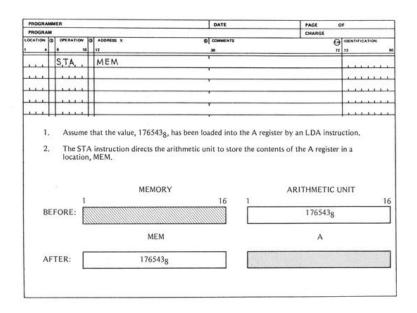

| Data Handling 78                                  | Enable Interrupt, ENB 110                      |

| Load A, LDA 78                                    | Inhibit Interrupt, INH 110                     |

| Store A, STA 78                                   | Halt, HLT 112                                  |

| Clear A, CRA 80                                   | No Operation, NOP 112                          |

| Interchange A and B, IAB 80                       | Unconditional Jump, JMP 112                    |

| Interchange Memory and A, IMA 80                  | Jump and Store Location, JST 114               |

| Input Keys, INK 82                                | Reset C Bit, RCB 114                           |

| Output Keys, OTK 82                               | Set C Bit, SCB 114                             |

| Load X, LDX 84                                    | Unconditional Skip, SKP 116                    |

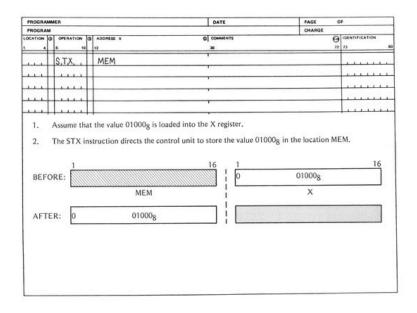

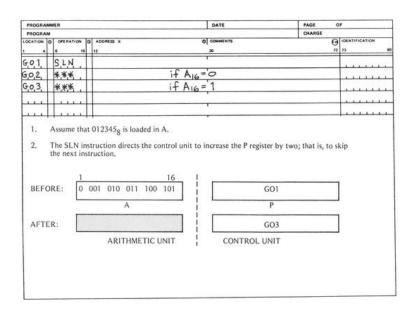

| Store X, STX 84                                   | Skip If Low-Order Bit One, SLN 116             |

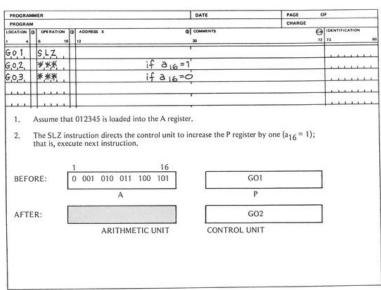

| Arithmetic 86                                     | Skip If Low-Order Bit Zero, SLZ 116            |

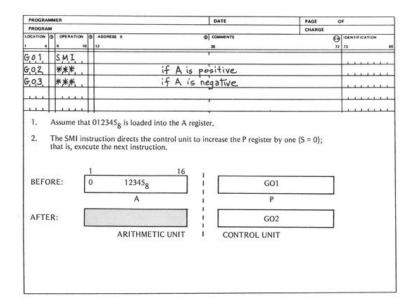

| Add, ADD 86                                       | Skip If A Minus, SMI 118                       |

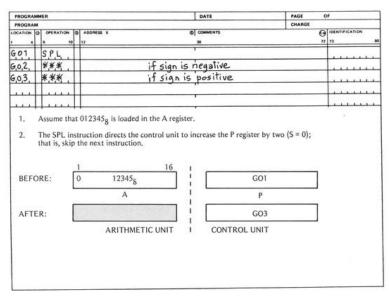

| Twos-Complement A, TCA 86                         | Skip If A Plus, SPL 118                        |

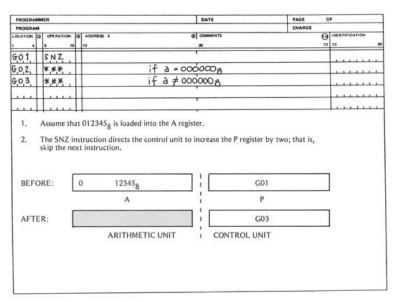

| Add C to A, ACA 88                                | Skip If A Not Zero, SNZ 118                    |

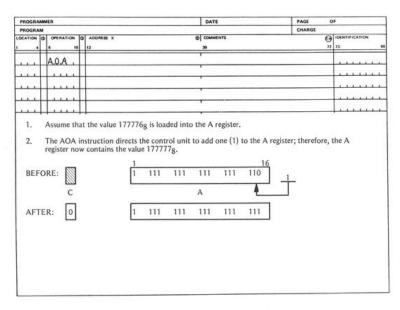

| Add One To A, AOA 88                              | Skip If A Zero, SZE 120                        |

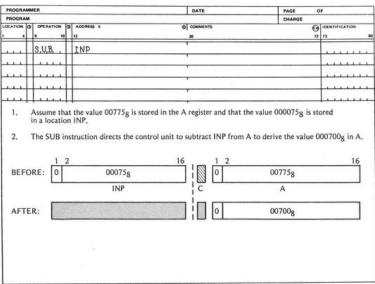

| Subtract SHR 88                                   |                                                |

| Skip If Sense Switch Reset, SRn 120<br>Skip If Sense Switch Set, SSn 120 |

|--------------------------------------------------------------------------|

| Skip If C Set, SSC 122                                                   |

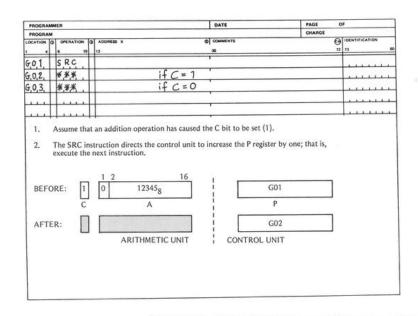

| Skip If C Reset, SRC 122                                                 |

| Skip If No Sense Switch Set, SSR 122                                     |

| Skip If Any Sense Switch Set, SSS 122                                    |

| Input/Output 124                                                         |

| Output Control Pulse, OCP 125                                            |

| Skip If Set, SKS 126                                                     |

| Input To A, INA 127                                                      |

| Output From A, OTA 128                                                   |

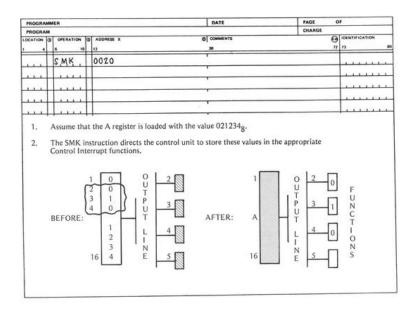

| Set Mask, SMK 129                                                        |

| Featured Capabilities 130                                                |

| Enter Double-Precision Mode, DBL 130                                     |

| Enter Single-Precision Mode, SGL 130                                     |

| Double Precision Load, DLD 131                                           |

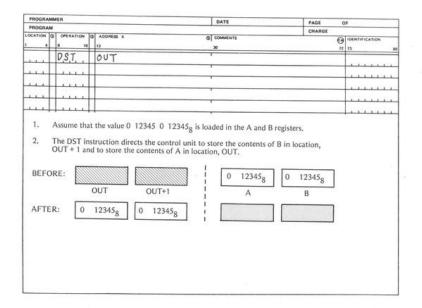

| Double Precision Store, DST 132                                          |

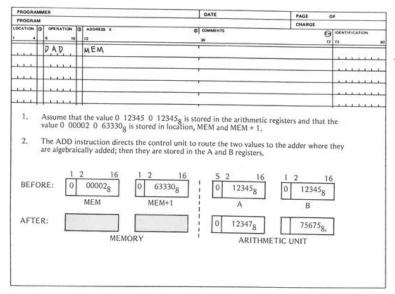

| Double Precision Add, DAD 132                                            |

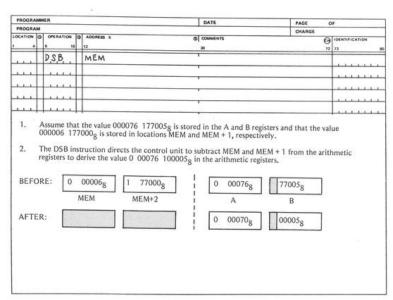

| Double Precision Subtract, DSB 132                                       |

| Multiply, MPY 134                                                        |

| Divide, DIV 134                                                          |

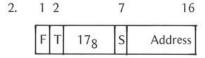

| Normalize, NRM 134                                                       |

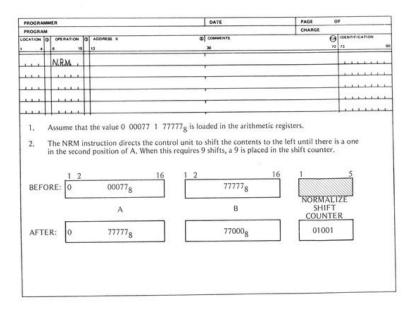

| Shift Count To A, SCA 136                                                |

| Memory Parity 137                                                        |

| Skip If No Party Error, SPN 137                                          |

| Skip On Memory Parity Error, SPS 137                                     |

| Direct Memory Parity Error, RMP 137                                      |

| Enable Extended Addressing, EXA 138                                      |

| Disable Extended Addressing, DXA 138                                     |

| Enter Restricted Mode, ERM 140                                           |

|                                                                          |

# LIST of ILLUSTRATIONS

| Figure 1 — Ratio of Project Cost Factors 2              |

|---------------------------------------------------------|

| Figure 2 – A System's Components 4                      |

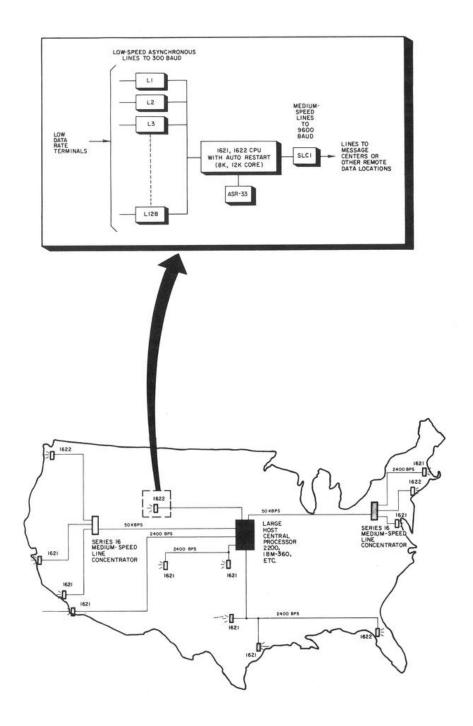

| Figure 3 — A Typical Message Switching System 7         |

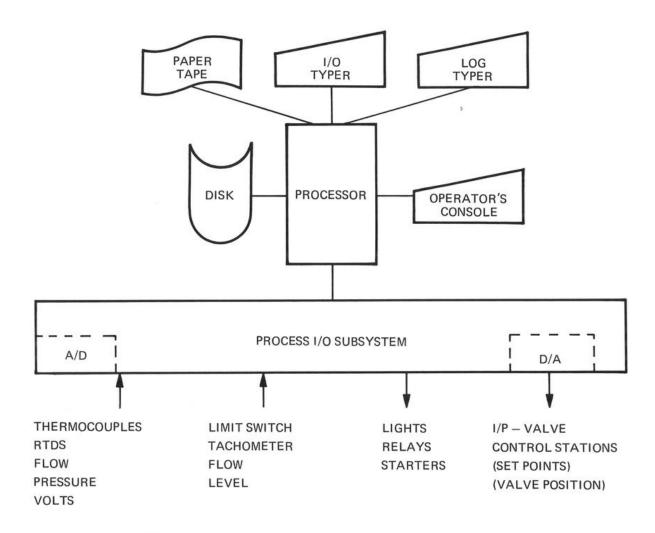

| Figure 4 — Typical Process Control Computer System      |

| Figure 5 — Typical Timesharing System 16                |

| Figure 6 – Series 16 System Components 17               |

| Figure 7 — Data Acquisition and Control System 20       |

| Figure 8 – Typical Model 1622 Application 23            |

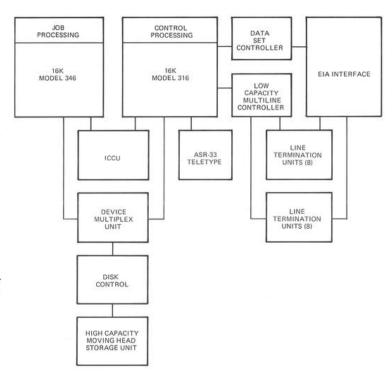

| Figure 9 – Model 1642 Timesharing System 24             |

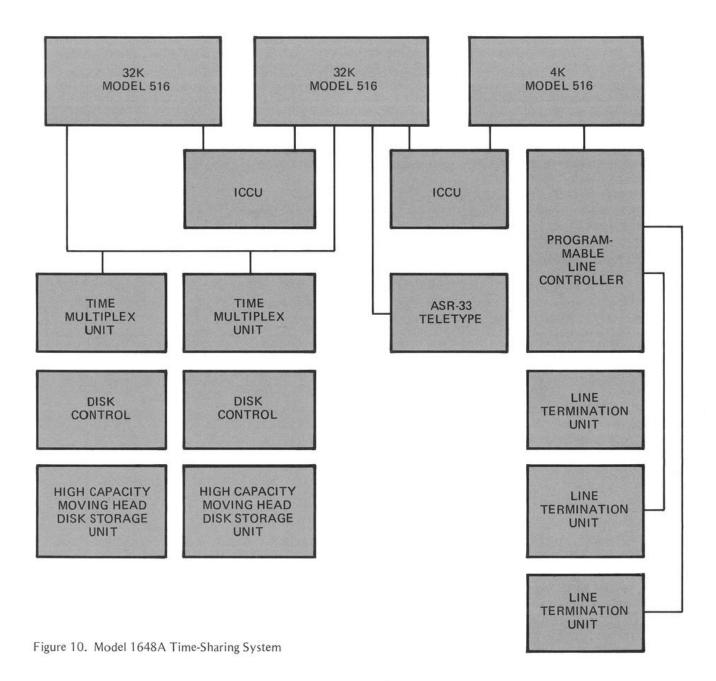

| Figure 10 - Model 1648A Timesharing System 27           |

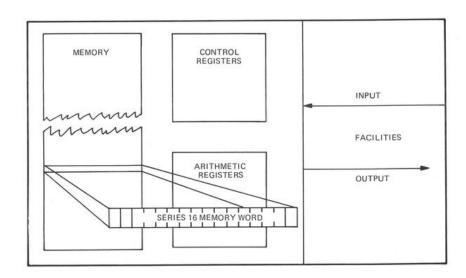

| Figure 11 — Logical Division of a Series 16 Processor 3 |

|                                                         |

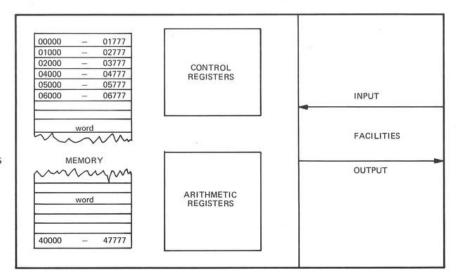

| Figure 12 - Address and Contents in a Series 16 Memory 36      |    |

|----------------------------------------------------------------|----|

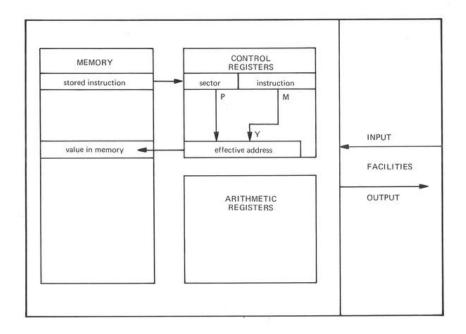

| Figure 13 — Typical Series 16 Control Register Activity 38     |    |

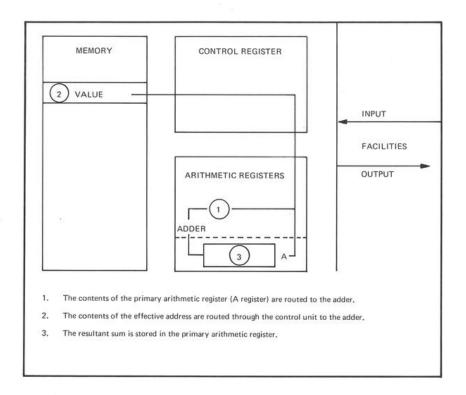

| Figure 14 — Typical Series 16 Arithmetic Register Functions 39 |    |

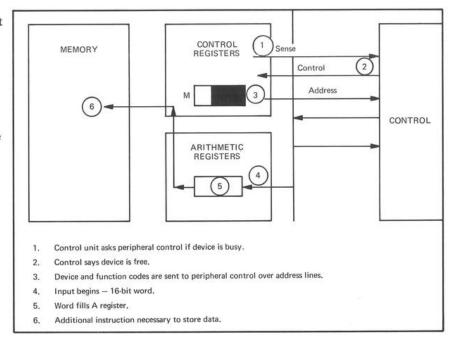

| Figure 15 - Single Word Transfer without Interrupt             | 40 |

| Figure 16 - Direct Multiples Control Input 41                  |    |

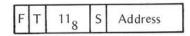

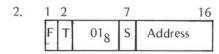

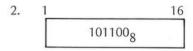

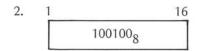

| Figure 17 — Series 16 Word Formats 45                          |    |

| Figure 18 - DACS - Model 8000 49                               |    |

| Figure 19 - Series 16 Communications Capabilities              | 66 |

# LIST of TABLES

| <b>Table 1</b> — Communication Systems Configuration Considerations 6        |

|------------------------------------------------------------------------------|

| Table 2 — Data Acquisition and Control System Configuration Considerations 8 |

| Table 3 — Heredity/Environment Suited to Today's Problems 13                 |

| Table 4 - Series 16 Course Availability 14                                   |

| Table 5 – Series 16 Features 15                                              |

| Table 6 – Summary of Series 1600 Capabilities 20                             |

| Table 7 – Summary of Series 1640 Capabilities 24                             |

| Table 8 — Summary of Ruggedized Systems Specifications 31                    |

| Table 9 – Configuring a Series 16 Processor 37                               |

| Table 10 – Summary of Processing Registers 38                                |

| Table 11 – Series 16 Instruction Repertoire 43                               |

| Table 12 — Summary of Data Line Controller Capabilities 51                   |

| Table 13 - Direct Access Capabilities 57                                     |

| Table 14 — Magnetic Tape Capabilities 59                                     |

| Table 15 – Series 16 Terminal Compatibility 67                               |

| Table 16 — Symbology 77                                                      |

## 1

## MINICOMPUTERS and INFORMATION PROCESSING

For the government, industrial, or educational analyst, consultant, and/or data processing manager, the 16-bit minicomputer is rapidly becoming a versatile, multipurpose answer to a host of information processing demands. Long recognized as an excellent tool in the process control environment (with tool the key word), its possibilities in a wider range of information processing applications (e.g., Data Communications, Computer System Timesharing, and even Batch Processing) have been recognized only recently.

Despite many claims, the "computer" is merely a tool, useful in information processing and control. Minicomputer users, from owners to operators, have long recognized that fact. Realizing that even in this era of instant answers, the rules of systems design (see insert below) are as valid as they were in the late days of patchboards and vacuum tubes, the minicomputer systems designer has consistently followed this formula:

# KNOW A TOOL'S CAPABILITIES BEFORE ATTEMPTING TO USE IT.

For many reasons, quite the opposite has occurred in the data processing-oriented segment of computer system manufacturing. Analysts and manufacturers have developed many stock, and therefore reasonably economical, answers to varied business processing problems; general accounting, and inventory control, among others. For the most part, such an approach to control

and communications problems was impossible. But, once the control and/or communication problems are outlined and certain general prerequisites concerning the capabilities of minicomputers are met, the solutions are available, economical, and often better, qualitatively, than those utilizing larger computers with a more general purpose.

Basically, the tools available (processors, interfaces, input/output subsystems, and the software that controls all three) merely manipulate data. Add it. Subtract it. Store it. Transfer it. To what advantage? Advantages include:

- The manipulation is fast.

- In comparison with human efforts, the manipulation is error free.

- The concept of the manipulation is easy to understand.

In fact, it is the simplicity of the 16-bit minicomputer design — its easy application to any problem — that is the minicomputer's strongest advantage. For this reason, especially in hard-to-pin-down process and communication applications, many consider the minicomputer a likely tool in implementing a solution. But remember, the tool is just one of the considerations, other factors in systems design are:

- Cost, and its cousin, time.

- Reliability among other specification requirements.

- Support provisions.

- The applications or procedures needing computerization.

Read and discuss these problem areas. Note and expand on the areas that most affect your situation. Then, discover the features and specifications that make the Honeywell Series 16 an excellent answer to many demands of the control and/or communications environment. Honeywell invites you to investigate this claim; your organization will demand it.

- 1. Understand the capabilities of available tools.

- Understand those procedures requiring control or processing.

- State the objectives of the control or processing project to be undertaken.

- Consider changes to the entire procedure as well as the application of a computer system.

- 5. Design the solution.

#### MONEY MATTERS

Whether you are in charge of budgeting a computer implementation effort or merely hamstrung by its budgetary constraints, you know that money matters. Every solution or application is a sum of parts, components, and despite claims to the contrary, each and every component has a cost. If you have to finish a project with a budget in mind, you had better peg that cost.

In budgeting total expenses, there's a tendency to overemphasize hardware prices. While there's no doubting mainframe and peripheral charges, the key parameters in implementing a minicomputer application as budgeted, involve:

- Software design and development

- Interfaces of all sorts.

- Support no matter who supplies it.

- People.

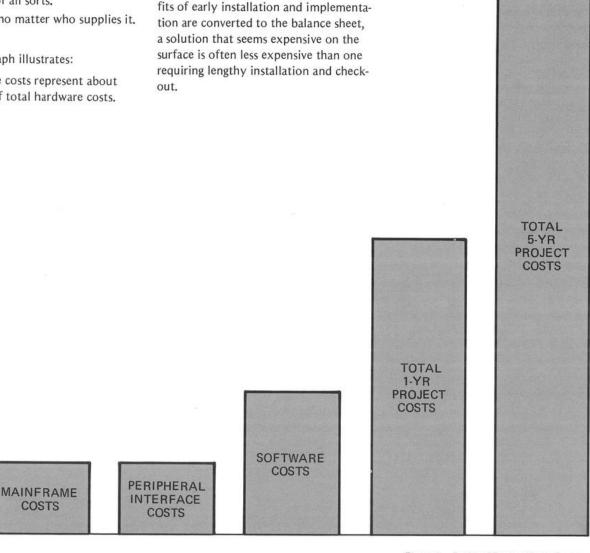

As the bar graph illustrates:

1. Mainframe costs represent about one-half of total hardware costs.

- 2. Mainframe costs represent about one-half of software costs.

- 3. Mainframe costs represent only about one-fourth of total first year invest-

- 4. Mainframe costs represent only oneeighth of the total cost of a five-year project.

And, unlike hardware costs, which are relatively fixed by competition in the market and the cost of production, the prices charged for software, support, and personnel, can vary widely.

#### Time Is Money

A final monetary consideration: time is money, too. Carefully weigh project costs and benefits as they relate to a time line. For example, once the benefits of early installation and implementation are converted to the balance sheet, a solution that seems expensive on the surface is often less expensive than one requiring lengthy installation and checkout.

Figure 1. Ratio of Project Cost Factors

#### RELIABILITY; SPECIFICATIONS, IN GENERAL; THE REAL WORLD

Because of either space age technology or the trend toward consumerism, or both, product reliability is a growing demand. No where is this more true than in the computer industry. But, in a cliche-ridden industry, "reliability" has been ridden into the ground. The fact that all manufacturers advertise their equipment's reliability is no reason to assume that one product is as reliable as the next. Such an assumption could prove disastrous in real-time applications like control or communications.

Engineers, specializing in this field, define product reliability as:

"... the probability that a given piece of equipment will perform a specified function, without failure, within a given period of operation, under given environmental conditions."

This is meaty material; not the stuff about which catchy jingles are generated. When, in careful systems design, objectives are stated, note the necessity and degree of required reliability. If it amazes you that there are degrees of reliability, be prepared to watch months of planning disintegrate during a brownout. In fact, to anticipate modes of failure is to increase the probability of a system's success.

Systems are a sum of many basically simple parts. They interact in a complex set of relationships in order to perform certain tasks. This is as true inside the processor and other hardware components as it is for the procedures themselves. If you're responsible for specifying these interrelationships, consider the reliability of such parts as the communications lines, the valves to be controlled, the people who'll enter control data, etc. Then, consider the reliability factor of the tools (components) to be used.

Many other specifications are involved in systems design. The analyst lists and relists the electrical, physical, and environmental conditions under which he expects his equipment to function. Again, as with reliability, there are degrees of ruggedization; remember that the ruggeder the environment specified, the higher the cost. This relationship between performance and cost can't be stressed too much.

For example, computer systems used in many large, batch-oriented applications are so sensitive that they require temperature and humidity measurements of minimal fluctuation. Other systems are tough enough to withstand great changes in temperature, humidity, altitude, barometric pressure, and even sustained shock. If you need special performance capabilities in any of these specification areas, the tools are available.

Finally, other specifications are specific to the application:

In control applications, parameters like voltage, hydraulic flow, and decibels may require measurement. Unless care is taken to match processor and interface capabilities to the capabilities of the measuring devices, even the most extensive data acquisition and control system is in for trouble.

In a minicomputer communications application, many factors affect final specifications: the terminals feeding the processor, the lines they can or must utilize, the choice of controller type, the input/output mode, and most importantly, the nature of the application. Within each one of these areas, a wide degree of performance specifications are available.

If this sounds confusing — to some degree — the confusion is intentional. By considering randomly so many of the performance/problem areas that exist in designing solutions, you can't help but be aware of the great complexity of it all. But the fact is, while there are real-world restraints like a budget and performance capabilities, there are also means of overcoming these problems. They include:

- Available support,

- Your knowledge of the applications, and

- The tools themselves.

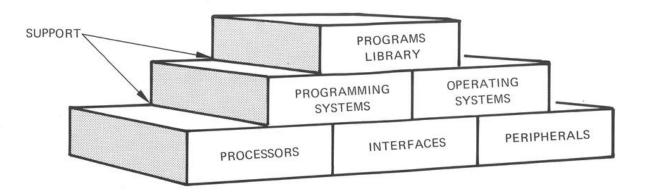

Figure 2. A System's Components.

Support can become a two-edged sword. Just as you can't confidently pretend to design, implement, and operate a minicomputer application without assistance, you must exercise full planning and implementation control over the implementation of a "turnkey" solution to one of your organization's processing problems. Probably, the greatest asset you possess is your knowledge of the procedure requiring computerization. This knowledge when combined with the kind of support you can and should seek from qualified consultants, computer manufacturers, and your own management, leads to successful application. The types of support available:

- Design support.

- Implementation support.

- Post-installation support.

All three are required in order to fully realize the potential of a project. All three are available in varying degrees and in, your systems design, the amount you expect should be specified.

#### Design Support

In the planning stages of a project, time is the one supporting ingredient which your management can supply. Because careful planning and the setting of objectives are so import-tant when an organization begins to tread on new ground (either the use of a computer system for the first time or the implementation of a new application on a currently installed computer system) every objective of the system must be carefully specified. This is accomplished by:

- Defining requirements; specifying the people needing the processed output or the device needing control.

- 2. Defining input methods; volumes, forms, formats digital, analog.

- Defining communication methods (if any); traffic, redundancy, terminals, tests.

- Defining data storage specifications; devices, file organizations, accessing methods.

- Defining processing methods; programming systems, operator actions, available routines.

- 6. Defining a control of the control system itself, and finally...

- Defining the plan under which implementation and post-installation will proceed.

As Figure 2. illustrates, support is the non-component factor that holds the

systems components (processor, input/output subsystems, interfaces, and software) together. Like an adhesive, it must be applied over the entire surface of the solution but not so heavy as to prevent their interaction. During planning the best source of support from consultants is the purchase of a study of your processing needs. When done properly, this is a worthwhile investment in your project's success.

Computer manufacturers offer extensive planning support, including many general and specific publications, and some excellent fee-charged and non-fee courses and seminars. When all three elements are combined, the designer is assured of having the proper knowledge of the problems he faces and the tools available.

#### Implementation Support

Implementation (or pre-installation) support, including software modules, systems analysis time, specific and often no-charge education, helps the organization over the rough period while new equipment is being installed and old systems are phasing out.

#### Post-Installation Support

Once installed, every system requires on-going user and manufacturer support to ensure the fulfillment of the performance and reliability objectives stated during the planning phase. Unless you're one of the "iron" organizations of the industrial community or the governmental superstructure, this type of on-going support will be a major concern. The best solution: a regular maintenance program of troubleshooting and systems test plus immediate response to down-time situations.

#### THE APPLICATIONS THEMSELVES

As tools, 16-bit minicomputers have special usefulness in the control and communications environments. Because of their size, cost, specification flexibility, and advantages (fast, accurate, design simplicity), minicomputer systems are limited only by the number of related problems your organization faces.

Generally, minicomputer applications are real-time, rather than batch, oriented. More specific indicators of minicomputer usefulness include:

- Problems that, though exceedingly complex in their entirety, can be reduced to small manageable components.

- The actual or possible overloading of a large-scale central computer.

- A requirement for uncomplicated, high-speed peripheral or interface throughput.

- Fast response to changing environmental conditions.

- A limited calculation application.

Remember, before going any further, that a minicomputer system is not an answer for all your information processing problems; not even for all your small information processing problems. Commercially-oriented systems designed to process large batches of related data at one time have superior characteristics (peripheral overlap, large main memory) in problem areas where the need for them exists and where the resources required for successful implementation are available. But, minicomputer systems with their special size and throughput characteristics meet the demands in the problem area (process control) for which many of them were designed. They are paradoxically, general-purpose systems that can be dedicated to one need while retaining a general nature.

#### **Data Communications**

The choice of the correct communications equipment in a particular

application hinges on both cost and specifications. As in all other minicomputer configurations, the components include processor, input/output subsystems, interfaces, and software; in particular, the interfaces will be communications line controllers, and the system itself will be a remotely-located peripheral of a central computer.

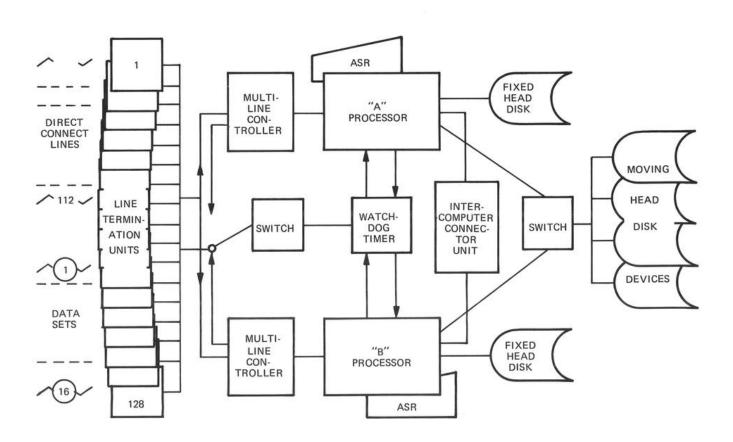

In many instances, 16-bit minicomputers have proven extremely effective in accomplishing communications tasks for which only large computersystems were suggested in the past. Message switching is one example. In the illustration on page 7 the two computers are handling the switching of messages between as many as 128 low-speed communications lines. Because their cost is so low, and the amount of actual calculation is small, the 16-bit computers used in the example offer the best solution to the budgetary problem faced in the example shown. Performance characteristics that make the minicomputer a useful tool:

- Extensive character manipulation.

- Character string checking.

- Real-time housekeeping.

All three are ideally handled by a small processor with a fast cycle time and high throughput capabilities. The use of two central processors also provides a redundancy factor that increases the systems reliability.

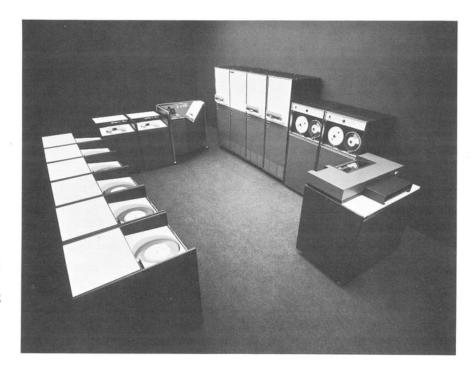

The peripherals used in the message switching application are also important factors in this solution's success. A proper balance between the high-access-time fixed head disks and the high-capacity moving head disks provides both immediate intransit and long term journaling and intercept storage.

The processor/peripheral array interfaces both the more versatile direct connect and the more economical switched network lines; such a capability is an important factor in holding down the costs of communicating, a cost element that is only partially affected by the central processor and peripherals chosen. These costs are fixed, according to the type of service, by the government and the common carriers who supply them.

In operation, the 128 separate lines feed partially formed characters into a multi-line controller that also offers the proper balance of performance and cost; that is, while meeting line speed specifications, they are more economical than separate data line controllers. The multi-line controller formats the characters, checks for parity, and performs other control functions before passing the characters on to the processors.

Input to both processors is simultaneous and in parallel; because of this capability, both processors build identical information on the intransit fixed head disk devices.

Interprocessor communication utilizes the ICCU (Intercomputer Communications Unit); this device enables redundant message processing. Another hardware factor, important to the reliability of the application, is the watchdog timer (WDT), an independent hardware device that monitors the performance of both processors and provides an alarm and switchover if one of the processors should fail.

Sophisticated software utilizes and controls the hardware configuration. It is this software that handles the constant tasks of blocking, error detection, code conversion, editing and routing which are the purposes of a message switcher.

Other communications applications for which the 16-bit minicomputer is an economical, reliable solution include:

■ Remote Concentration — A system, located at a distance from the central computer, accepts data concurrently from multiple low speed lines and concentrates this data for

TABLE 1. COMMUNICATION SYSTEMS CONFIGURATION CONSIDERATIONS

| Consideration                           | Requirements                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-, Dual-, or Multi-<br>Processor? | Dual processors are important where any of these factors are pre-eminent:  — load sharing                                                                                                                                                                                                                                               |

|                                         | <ul><li>reliability</li><li>maintainability</li></ul>                                                                                                                                                                                                                                                                                   |

|                                         | Where these requirements are not pre-eminent, a single-processor control system can be specified with resulting savings.                                                                                                                                                                                                                |

| Controllers?                            | Controllers available to the systems designer:                                                                                                                                                                                                                                                                                          |

|                                         | <ul> <li>single line</li> <li>high- and low-capacity multi-line</li> <li>programmed multi-line</li> </ul>                                                                                                                                                                                                                               |

|                                         | Usually chosen before any other hardware component, the choice of controllers is based on the desired mix of line speeds, the need for synchronous or asynchronous transmission, the use of private line or the switched network, the types of timing and direction (simplex, full or half duplex), and finally, future plans.          |

| Types of Communications Lines?          | Usually your application and the terminals that are a part of that application will determine lines required. In general, there are three categories:  — under 300 bps - low speed  — between 300 and 9600 bps - medium                                                                                                                 |

|                                         | - 9600 bps and above - high speed                                                                                                                                                                                                                                                                                                       |

|                                         | The important element for the designer is the configuration of an economical mix of lines within the requirements of your application.                                                                                                                                                                                                  |

| Processor Interface?                    | The mode of processor interface (single word, block transfers of data, direct memory connection) is an important design consideration. These modes are normally extra cost items on a processor; first of all be sure they are available; secondly, be sure you don't have to pay extra for a capability your application doesn't need. |

| Line Interfaces?                        | The choice of line interfaces depends on the choice of terminals. Single line controllers require no interface at all; interface is integral within the controller. Multi-line controllers have a specified interface keyed to their specifications.                                                                                    |

transmission over a single high speed line to the central site. This system is most useful where geographical distance demands a single low cost line in place of many high cost lines. The remote concentrator itself is located in the approximate center of the many low speed lines.

■ Remote Batch Terminal — The simplest communications application, the remote batch terminal provides remote input and output of batches of data over a single communications line; depending on available software, the use of a minicomputer, rather than a hard-wired terminal, gives the user the option

- of off-hour data processing.

- Multiplexer In many cases, the minicomputer may prove the best method of performing the same function performed by the multiline controller in the message switching illustration. Because of its software capabilities, it is able to perform intelligent character assembly/disassembly, transfer, control recognition, and other tasks associated with communications interface.

- Message Controller In this application, the minicomputer or minicomputers would perform one or

- all of the above applications in association with a central computer. Functions include:

- Terminal polling and addressing.

- Line buffering.

- Automatic logging and routing.

- Line and network status reporting.

- Message security and header control.

The concept of relieving the central computer of all communications functions is the goal.

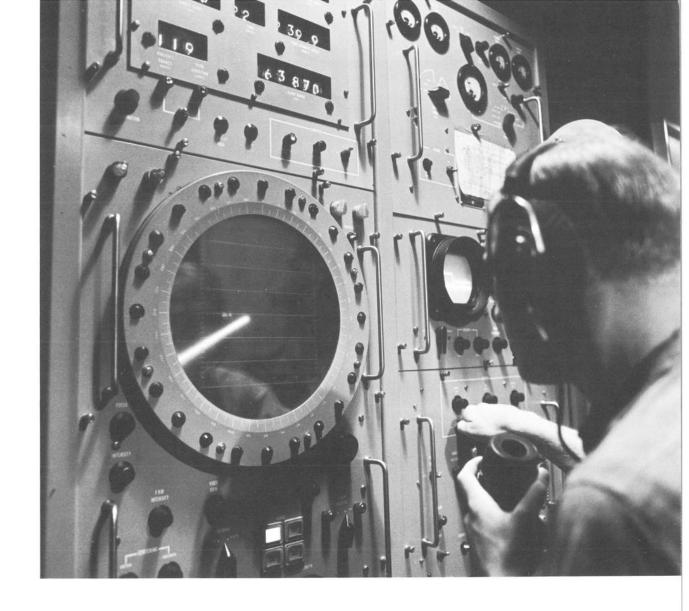

Figure 3. A Typical Message Switching System.

#### Data Acquisition and Control

Interface capabilities are the keys to data acquisition and controls system design. The systems themselves may vary from the simple recording of many data measurement devices to the sophisticated use of the minicomputer in order to acquire data, test its status against some norm, and branch to control instruction that would direct further actions by the procedure under computer control. The possibilities are only limited by the number of procedures that exist in industrial, and governmental applications.

TABLE 2. DATA ACQUISITION AND CONTROL SYSTEM CONFIGURATION CONSIDERATIONS

| Consideration                      | Requirement                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor?                         | In a control application, the processor should possess extended accumulator capabilities and high-speed addressing capabilities, especially indexing.                                                                                                                                                                                                                                             |

| Peripherals?                       | The peripherals associated with a data acquisition and control system should provide economy and a good balance of bulk storage, input, and output devices in addition to the Process I/O Subsystem described below.                                                                                                                                                                              |

| Bulk Storage?                      | With a choice between fixed and moving head disks or magnetic tape, the considerations are these:                                                                                                                                                                                                                                                                                                 |

|                                    | <ul> <li>Fixed head disks provide high speed access and relatively low capacity capabilities.</li> <li>Moving head disks, on the other hand, provide a high storage capacity with a slower access time.</li> <li>Useful where storage follows some fixed sequencing order, magnetic tape devices are even less expensive than disk devices.</li> </ul>                                            |

| Input?                             | Input peripherals include paper tape and punched card devices. Paper tape devices are usually less expensive, more difficult to change once a program tape has been prepared. The more expensive punched card devices permit the simplest program patching.                                                                                                                                       |

| Output?                            | For printed output, the quantity determines an application's need for a high-speed line printer. In every case, a teletypewriter should be specified because of its usefulness as a control device.                                                                                                                                                                                               |

| Process Input/Output<br>Subsystem? | <ol> <li>The process input/output subsystem:</li> <li>Selects and conditions input and output signals from the interfaces.</li> <li>Buffers and times the signals.</li> <li>Protects the central processor from excessive voltage intake from the various control devices.</li> </ol>                                                                                                             |

| Analog Inputs?                     | The choice of high and low level analog inputs rests on the requirements of the specific system being designed. Input modules are available to take practically any mix of thermocouple, control signal levels and outputs from process sensors such as flowmeters, pressure tranducers and others, with full scale ranges from plus or minus a few millivolts, up to 115 Vac, or current ranges. |

TABLE 2. DATA ACQUISITION AND CONTROL SYSTEM CONFIGURATION CONSIDERATIONS (Cont.)

| Consideration             | Requirement                                                                                                                                             |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Inputs?           | The digital inputs to a process control system can be used to inform the processor of:                                                                  |

|                           | - status (on or off, etc.)                                                                                                                              |

|                           | <ul> <li>asynchronous (a condition of many ons and offs)</li> </ul>                                                                                     |

|                           | - count (the number of ons and offs)                                                                                                                    |

| Digital Output?           | The processor can direct a flip/flop (set/reset) signal or a single-shot signal to the process being controlled                                         |

| Digital/Analog Converter? | Often as a cost consideration, the output of a digital/<br>analog converter will be multiplexed so that no more<br>than one converter will be required. |

Figure 4. Typical Process Control Computer System

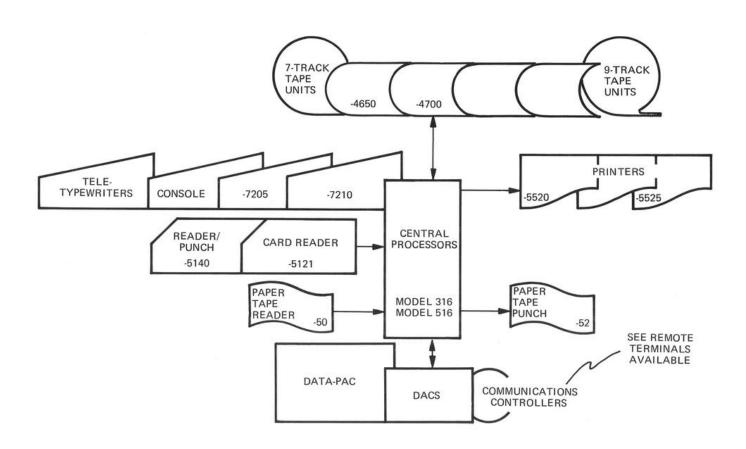

Figure 5. Typical Time Sharing System

Time sharing, both a communications and a control application because it involves the control of computer time as shared by a number of remotely located users, is a rapidly growing area of minicomputer application. In its earliest usage, time sharing involved only large-scale computer systems.

Now, this is changing. Some of the advantages these systems offer include:

- Computer access is virtually simultaneous with demand and therefore, for all intents and purposes, the computer is your own.

- Remote access is usually, but not always, performed on an easy-to-use keyboard; this replaces bulky and unfamiliar punched cards.

- Problems are solved in an interactive mode as opposed to the batch mode used by most in-house shops.

■ The concept of time-sharing is ideally suited to the rapidly growing field of data base management.

Time sharing, in fact, is an already accepted solution to the problem many business-oriented organizations face when their employees interface with the computer. In many cases, the users pay for this "man/machine rapport" in everincreasing monthly fees; sometimes these fees are higher than the cost of a wholly-owned batch system. Where this important economic factor is true and the user still desires the convenience and capabilities of time sharing, a solution even more economical than the batch system, 16-bit minicomputers, is available. With a well-designed minicomputer-based time sharing system, many manufacturing, governmental, and educational users can retain the advantages of the time sharing service while gaining:

- A system specialized to specific company needs instead of a system that satisfies the needs of an entire network.

- A wide choice of processing capabilities.

- Proprietary information never leaves the company.

- Interaction with the organization's batch system, if there is one, is easier if a time sharing system is also in-house.

- There is only one price; fees do not vary depending upon the number of time sharing services used by the organization.

Traditionally, time sharing is considered a system suited to educational and research facilities. In fact, time sharing is an economical answer to problems in any organization that needs the advantages mentioned above. Time sharing is currently utilized in a wide number of industries and applications areas, including manufacturing, printing and publishing, engineering, management science, financial management, personnel, and administration.

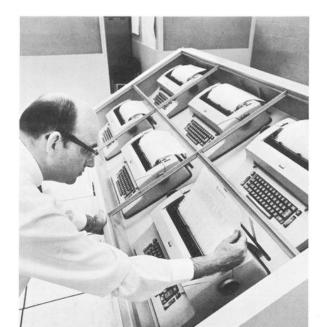

Many time sharing systems utilize a single minicomputer; more advanced systems use up to three separate central processors and still provide a price/performance break when compared with batch computer systems programmed, rather than designed, to provide time sharing. Again, as with control and communications applications, the determining factors, when specifying the caliber of time sharing system needed in your installation, are the specifications desired, the degree of reliability required, the number of users served, the budget restrictions, and support provisions.

Figure 5 illustrates a larger mini-computer system that services up to 64 simultaneous (others non-simultaneous) terminal users with programming capabilities limited only by the type of software the user chooses or chooses to develop.

Terminal input is handled immediately by a 16-bit processor with 4K main memory. The machine transfers characters to and from the terminals, provides echoback for transmission verification, provides some buffering, and enters characters one at a time into the control processor. The control processor and the job processor both share moving head disk files for data interchange; these two processes exchange/control information through an ICCU. The control processor, essentially the executive of the system, provides the normal interaction between the user, his programs, and data files that are held on the disks. The user may build up programs and data files upon the disks and when he requests that these programs be run, the control

processor will queue his request for execution on the job processor. When the job processor is ready to execute the program, it will read the necessary files from the disks and input any required system programs from the system disk. Then, it will clock time, for a predetermined period; and if the job has not been completed, output the unfinished job to the system disk.

In this minicomputer application, the tasks have been divided evenly between the three processors. There is considerable difference in the computing power of the machines, each machine being matched reasonably well to the task required of it. The communications processor is a short cycle time, small memory, 16-bit processor, while the control and job processors are both large core capacity processors. The use of the multiple processor configuration has considerably increased the power of this system over an equally priced processor designed originally for batch data processing. Its design has simplified the task of implementing the software and of adding modifications, important factors in a growing installation.

As a simple example of the independent usage of the processors, the control and job processors can be isolated from the normal time sharing function and used for software development by the systems programmers, while the front end communications processors remains on-line to terminal users. Clearly the terminal users cannot do their normal computation, but when they attempt to sign on, the communications computer can reply with a standard message informing them of the state of the system.

#### THE TOOLS, THEMSELVES

The ability of the Series 16 to solve difficult control or communications problems is well documented. Aboard ship, in flight, in line, in real-time — the buzz words of tomorrow's applications — are design factors in Series 16 application today. This is no accident, the Series 16 is suited by heredity and environment to the problems of the future.

The Honeywell Series 16 includes systems components, tools, of each type:

- Central Processors

- Input/Mass Storage/Control/Output Subsystems

- On-Line Interface

- Software Systems

In addition, Honeywell supplies support that the rest of the minicomputer manufacturers can only envy. Its elements include:

■ Education facilities from the only minicomputer manufacturer who is in the computer education field.

- Complete documentation, hardware and software, to support system design, installation, operation, and maintenance.

- A wide-area systems analysis and field service organization.

Most importantly, the Series 16 allows different modes of solution, including, on one hand, complete applications systems that save both time and money and, on the other, individual DATA-PAC products from which an entire system could be custom built, piece-by-piece. More specifically:

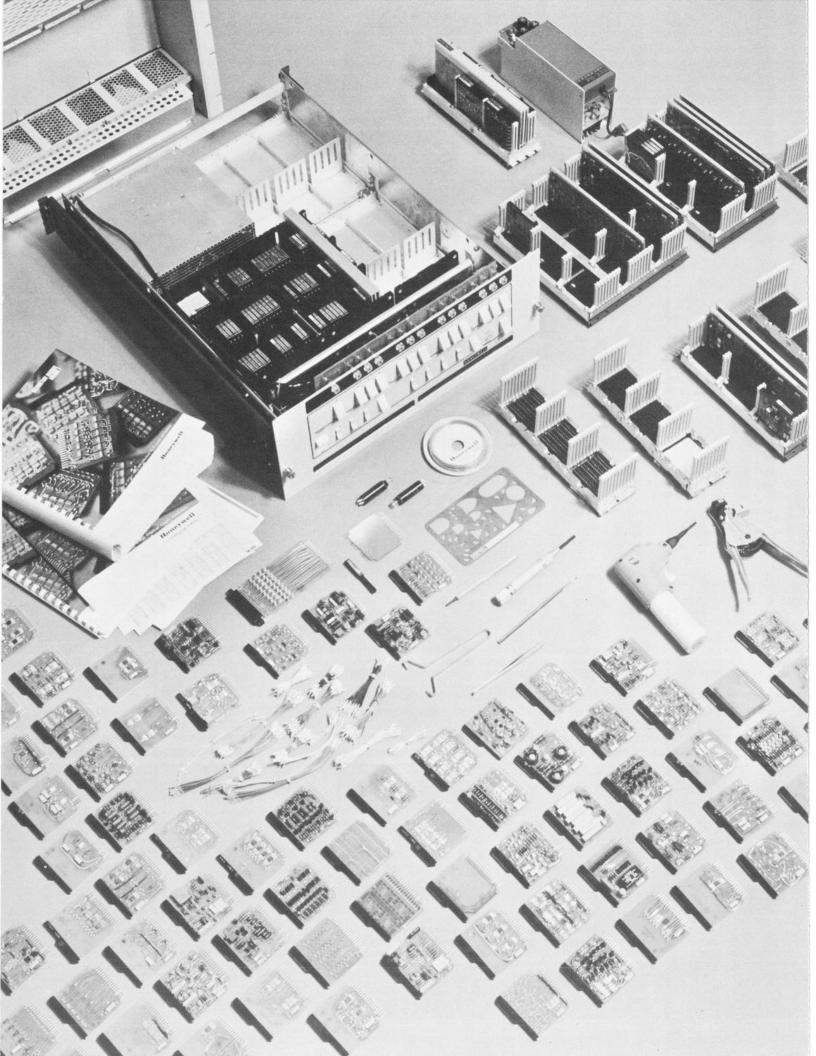

"'building blocks" — systems components, completely checked out, from which a system designer can, with confidence, assemble a solution best suited to his particular problem.

or

"total solutions" — complete applications systems, answers to well defined and often-confronted problems for which the Series 16 is an excellent solution.

Like the selling features of the Series 16's many products, the choice of a kind of solution, associated with the Series 16, is an example of the Series 16's greatest asset: THE SERIES 16 IS A PRODUCT OF THE REAL WORLD.

#### What Are the Tools?

#### **PROCESSORS**

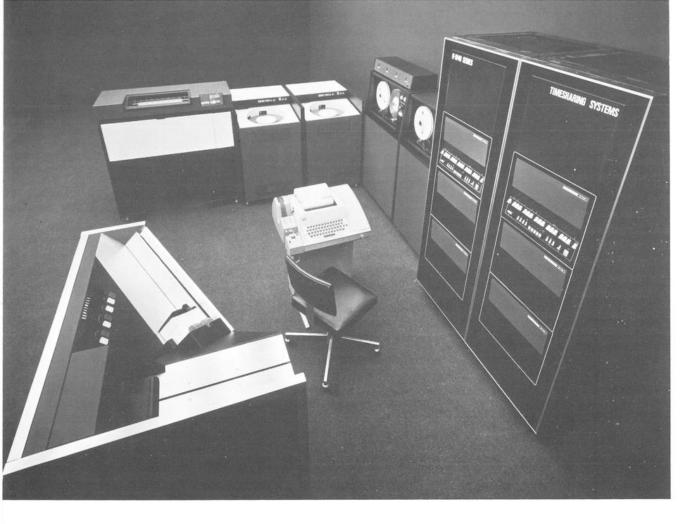

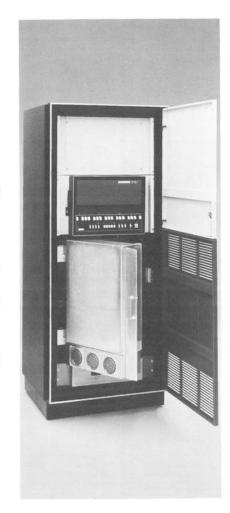

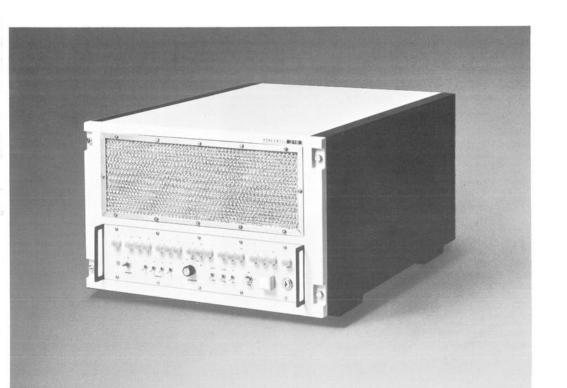

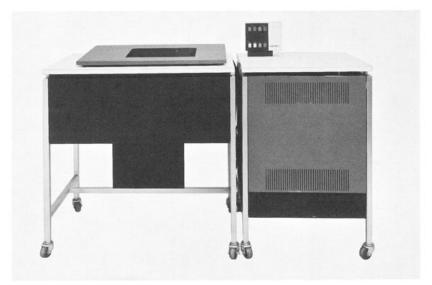

Honeywell's latest Series 16 products include two general-purpose, integrated circuit, digital central processors, the Models 316 and 516. Each features design and specification characteristics, as well as a price tag, that makes them suitable to similar, yet specifically different, minicomputer applications. The low-priced Model 316 offers the systems designer the economy features that make many applications viable; as well as offering full Honeywell support. The Model 516, with a faster cycle time and increased peripheral throughput capabilities, also offers full support capabilities and a price as attractive as its advanced performance specifications.

TABLE 3. HEREDITY/ENVIRONMENT...SUITED TO TODAY'S PROBLEMS

| Heredity                                                                                                     | Environment                                                                                                                |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Descendants of the 116, the indus-<br>try's first 16-bit computer.                                           | "Total" Honeywell support embraces all Series 16 products.                                                                 |

| Born of the best components pro-<br>duced by people who began pro-<br>ducing components.                     | <ul> <li>Used extensively by Honeywell,<br/>the world's leading automation<br/>company, in internal application</li> </ul> |

| <ul> <li>Featuring technical refinement and<br/>reliability standards that are second<br/>to-none</li> </ul> |                                                                                                                            |

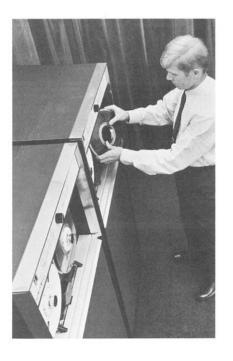

#### INPUT/STORAGE/CONTROL/ OUTPUT

The second element, the Series 16 peripheral complement, is one of the most complete in the minicomputer field. No matter what an application demands in terms of data input control, mass storage, or output, the Series 16 features a peripheral that suits the requirements. Input devices available include: card readers, paper tape readers, and console keyboards. The console, as well as the teletypewriter and visual information projection (VIP) options featured in the Series 16, are also useful control devices. Disk devices, with both fixed and moving heads, are available for direct access mass storage and the more economical magnetic tape subsystems enable mass storage where a sequential processing mode is established. Output devices include a paper tape punch, card reader/punch, and a line printer. All Series 16 peripherals are supported by the Series 16 software systems and each features peripheral overlap and error checking controls that reflect the design status of the Series 16 processors.

#### **INTERFACES**

On-line interfaces, the modules that enable the Series 16 to be effective in

all types of specific control and communications areas, including hybrid or one-time applications, also make the Series 16 a leading choice for the systems designer. Interfaces available:

- Data Acquisition and Control Subsystems two complete families of compatible products permit interface with various voltage levels and signal types.

- Communications Controllers three general speeds and from one to 128 lines can be controlled by an assortment of single-line, multi-line, and programmed multi-line controllers; an assortment of other features permitted.

- DATA-PAC Family using the DATA-PAC family, the designer can build his own interface (as well as his own complete computer system, if he desires) from a completely compatible choice of components.

#### **SOFTWARE**

Sophisticated software, including both effective operating systems and powerful program languages, is an important Series 16 component. The operating systems feature the kind of effective control that reduces operator intervention and increases the system's efficiency. The available compilers give the Series 16 user the programming flexibility that ensures maximum utilization of the hardware. As with the other Series 16 components, software solutions are available in both general problem areas — control and communications. For programming the Series 16:

- An efficient, easy-to-use assembly language, DAP-16

- The industry standard, Fortran IV, useful in scientific applications.

- BASIC, TEACH, and SOLVE, three language systems suited to time sharing's simplicity requirements.

All software includes techniques necessary for sectorizing and loading in a small core memory processor. Unless noted, all hardware configurations are supported by the software; a Series 16 user is never forced to buy devices he otherwise doesn't need.

#### TABLE 4. SERIES 16 COURSE AVAILABILITY

| Length            | Title                                                                          | Objectives                                                                                                     |

|-------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Logic/Mai         | intenance Courses                                                              |                                                                                                                |

| 1 week            | Basic Computer Theory                                                          | Provide "building blocks" understanding.                                                                       |

| 5 weeks           | Series 16 (Models 316/516)<br>Logic/Maintenance                                | Provide student with working knowledge of Series 16 hardware, diagnostic programming, and computer operations. |

| Programm          | ning Courses                                                                   |                                                                                                                |

| 1 week            | Introduction to Programming                                                    | Introduce programming concepts.                                                                                |

|                   | Series 16 Programming                                                          | Provide working knowledge of: a. DAP-16 Assembler                                                              |

| 2 weeks<br>1 week | (Standard)<br>(Accelerated)                                                    | b. Loaders c. Utility routines d. Fortran IV Compiler e. Checkout routines f. Libraries                        |

| 2 weeks           | OLERT                                                                          | Teach Fortran programmers how to use OLERT.                                                                    |

| 1 week            | OP-16                                                                          | Teach Series 16 user how to utilize OP-16                                                                      |

| 1 week            | Series 16 Fortran                                                              | Provide sophisticated training in Fortran IV                                                                   |

| Periphera         | and Interface Courses                                                          |                                                                                                                |

| 2 weeks           | Series 16 Real-Time Interface                                                  | Working knowledge (operation, programming, and maintenance) of RTI                                             |

| 8 days            | Honeywell/CDC Magnetic<br>Tape (7- and 9-track) and<br>(VLC)                   | Knowledge of device and control logic and electromechanics, and programming techniques.                        |

| 6 days            | Honeywell Card Reader                                                          |                                                                                                                |

| 10 days           | Honeywell Line Printer                                                         |                                                                                                                |

| 8 days            | Honeywell Card Reader/<br>Card Punch<br>Type 273 Disk Moving<br>Head Disk File |                                                                                                                |

| Other Co          | urses                                                                          |                                                                                                                |

| 1 week            | Series 16 Interface                                                            | Present in-depth discussion of the Series 16 architecture                                                      |

| 1 week            | Series 16 Systems                                                              | In-depth discussion of the Series 16 capabilities; suited for management and design personnel                  |

| 1 week            | Series 16 Communications                                                       | An overview of communication techniques.                                                                       |

#### Support

The cohesive factor in systems structure, a factor that tends to hold a system together, support is one of Series 16's strongest facets. Featuring Education, Data Centers, Systems Support, Field Maintenance, Publications, Honeywell offers wide ranging and on-going support for all a system designers objectives. Specifically:

#### **EDUCATION**

To assist customers during both the planning and implementation phases of systems design, Honeywell offers a full array of programming and maintenance courses. The facing table lists the courses offered and notes their prerequisites; as always, other pertinent information is available from your Honeywell representative. Two training centers, one in Framingham, Mass., and the other in Sherman Oaks (Los Angeles), California, offer the same high quality educational atmosphere and teaching philosophy. The needs of some specific customers are met by the DSO Education Center in Arlington, Virgina. If you wish to enroll in any of the courses listed here or would merely like more information concerning them, indicate your interest on the Systems Designer Reply Card in the rear of this description.

#### **PUBLICATIONS**

A complete and up-to-date documentation package supports the installation and design of every Series 16 product or system. Both engineer-oriented and programmer-oriented documents on the following products:

- Processor and internal options.

- Peripheral devices.

- Operating systems and other software.

- Any special packages.

Most importantly, you get clear concise answers about many of the problems particular to systems design or you get only the documentation needed to support your particular installation; it's your choice.

#### TABLE 5. SERIES 16 FEATURES

| Communications                                                                                                                                                                                                                                                             | Control                                                                                                                                                                                                                                                                     |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Watchdog Timer — an optional capability that causes a program controlled interrupt if occurrence is monitored.                                                                                                                                                             | Cathode Ray Tube (CRT) Devices -<br>together with the teletypewriter, ex<br>cellent man/machine interface de-<br>vices.                                                                                                                                                     |  |  |

| Direct Multiplex Control — Direct Memory Access — these optional input/output modes enable processing concurrent with direct data flow to and from the controller.  Fast Internal Cycle Time — ensures complete message processing even with the highest throughput rates. | On-Line Interfaces — a complete selection of data acquisition and control as well as custom-designed interfaces permit certain control over a wider range of analog and digital inputs and outputs.  High Internal Cycle Time — ensures speedy response to external events. |  |  |

| Interrupt Facilities — allows branching, as necessary, between main program flow, and real-time service routine.                                                                                                                                                           |                                                                                                                                                                                                                                                                             |  |  |

| Multilevel Code Handling — translates, under program control, codes of up to 8 levels.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                             |  |  |

#### DATA CENTERS

Honeywell maintains Series 16 Data Centers throughout the United States. Each contains a typical Series 16 configuration and serves the needs for all of our customers for a program development system prior to system delivery. Usually, there is no charge. For more extensive work, machine time is available on a per-hour-charge basis. Either way, the design of the Series 16 assures the user that programs designed to run on one Series 16 system will run on most similar systems without any drastic changes.

#### SYSTEMS SUPPORT SERVICE

For every Honeywell salesman, more than ten other professionals are in reserve ensuring the user of complete support. Some of these support professionals, include the field service engineers who maintain installed Series 16 systems. During the design and implementation phase of systems design, support analysts and engineers are available for consultation on general and specific tasks. Or, if you desire, specific tasks will be completed by the engineers on a fee basis with or without user assistance.

#### FIELD MAINTENANCE

Maximum up-time is the result of Honeywell's extensive field support capability for the Series 16. This field maintenance organization allows Honeywell to insure reliability and maximum performance for the one monthly rental. And every product, whether it is a single-component or an entire system, gets exactly the amount of maintenance it requires.

#### What Can the Tools Do?

Several features of the Series 16 hardware complement make it especially suited to the two major minicomputer application areas. The table below defines these factors. Some, though keys to the Series 16 application in one area, are actually general parameters, important in all.

#### **SERIES 16 SOFTWARE**

Figure 6. Series 16 System Components

## 2

# SERIES 16'S TOTAL SOLUTIONS

Total solutions save time and money. For the project or company under severe budgetary constraints, a Series 16 Application System might spell the difference between this year and next. Even for designers with the budgetary and personnel resources to implement their own solutions, the Series 16 applications systems:

- Put a project on-the-air sooner than otherwise possible.

- Free available manpower for other projects.

- Permit budget allocation flexibility in terms of both

- present or proposed systems expansion, and

- new systems development.

The Series 16 Application Systems are complete hardware/software/support packages combined to solve a variety of well-defined problems for which the Series 16 is an especially useful solution. Their easy and economical implementation and efficient operation combine to give a user the basic tools needed to perform the most complex functions.

Each package contains the Series 16 central processor that best does the required job in terms of computing power and economy. That is, just as an independent consultant or a staff designer would do, the Honeywell systems personnel have carefully weighed the capabilities and costs of the Models 316 and 516, and chosen, in each case, the hardware configuration best suited to the application.

Furthermore, each package utilizes the same flexible software systems available on all Series 16 processors. Not

only does this factor ensure quality programming and the best application of the hardware's capabilities but it also enables the user to expand systems software at his own pace.

Finally, the complete maintenance and support structure of Honeywell backs the user of the Series 16 application systems. Included is the training required to fully implement each system and the on-going maintenance required to ensure maximum system up-time.

As discussed earlier, the Series 16 is especially suited to applications in the control and communications environments. In answering internal Honeywell (remember that the other half of the The Other Computer Company is the world's foremost automation company) or specific customer demands, Honeywell systems designers have developed applications sytems for the following environments:

- Data Acquisition and Control

- the Models 1602, 1603, and 1605.

- Remote Message Concentrators

- the Models 1621 and 1622.

- Time-Sharing Systems

- the Models 1642 through 1648A.

- Clinical Laboratory Systems

- from Honeywell Data Systems Operations.

- Ruggedized Systems

- the Models 316R, 516R, and 1602R.

The development of systems in these and other categories is an on-going objective of the Series 16 design team.

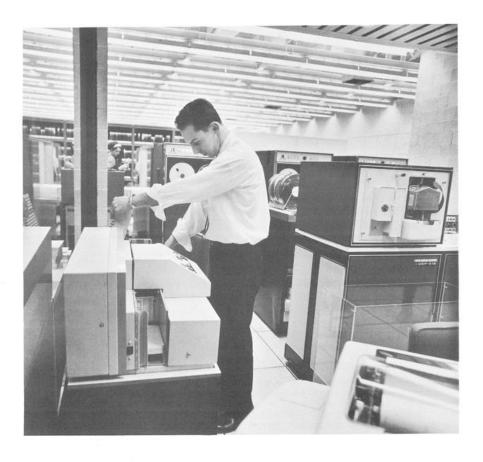

# DATA ACQUISITION AND CONTROL SYSTEMS

While the fully-developed data acquisition and control systems meet separate capability requirements, each contains three basic components:

- Series 16 hardware the central processor and peripherals needed to process and report on the acquired data.

- Real-Time Interface the specialized hardware required to easily interface with a wide variety of data acquisition devices; e.g., sensors, logic signals, control elements, displays.

- Series 16 software the operating system best suited to the application's need for data acquisition and control coordination.

Depending on the application, the data and control systems use either a standard or ruggedized 316 or 516 central processor. The Real Time Interface (RTI) regulates all signals between the monitoring and control elements of the external devices and the central processor. Each RTI:

- Decodes input and output instructions from the central processor and connects the selected input and output lines for data transfer.

- Conditions input signals.

- Converts analog input signals to digital form and digital outputs to analog form.

- Provides additional typewriters for logging data and alarm messages.

- Converts signals from computer levels to easily usable voltages and currents.

- Protects the CPU, the common or time-shared portion of the RTI, and related equipment from high-voltage faults in the field wiring between the customer plant and the RTI.

The features that apply to the Model 1602, 1603, and 1605 Data Acquisition and Control systems, design features found in few manufacturer's product lines, include:

TABLE 6. SUMMARY OF SERIES 1600 CAPABILITIES

| 1602                                                                                                                                                                                               | 1603                                                                                                                    | 1605                                                                                                                                                                                                                                                                                                                                |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|